# Field-Effect Transistors from Lithographically Patterned Cadmium Selenide Nanowire Arrays

Talin Ayvazian,<sup>†</sup> Wendong Xing,<sup>‡</sup> Wenbo Yan,<sup>§</sup> and Reginald M. Penner<sup>\*,§,†</sup>

<sup>†</sup>Department of Chemical Engineering and Materials Science, University of California, Irvine, California 92697-2700, United States <sup>‡</sup>Department of Physics and <sup>§</sup>Department of Chemistry, University of California, Irvine, California 92697-2025, United States

**ABSTRACT:** Field-effect transistors (NWFETs) have been prepared from arrays of polycrystalline cadmium selenide (pc-CdSe) nanowires using a back gate configuration. pc-CdSe nanowires were fabricated using the lithographically patterned nanowire electrodeposition (LPNE) process on SiO<sub>2</sub>/Si substrates. After electrodeposition, pc-CdSe nanowires were thermally annealed at 300 °C × 4 h either with or without exposure to CdCl<sub>2</sub> in methanol—a grain growth promoter.

The influence of  $CdCl_2$  treatment was to increase the mean grain diameter from 10 to 80 nm as determined by grazing incidence X-ray diffraction and to convert the crystal structure from cubic to wurtzite. Measured transfer characteristics showed an increase of the field effect mobility ( $\mu_{eff}$ ) by an order of magnitude from  $1.94 \times 10^{-4} \text{ cm}^2/(\text{V s})$  to  $23.4 \times 10^{-4} \text{ cm}^2/(\text{V s})$  for pc-CdSe nanowires subjected to the CdCl<sub>2</sub> treatment. The CdCl<sub>2</sub> treatment also reduced the threshold voltage (from 20 to 5 V) and the subthreshold slope (by ~35%). Transfer characteristics for pc-CdSe NWFETs were also influenced by the channel length, *L*. For CdCl<sub>2</sub>-treated nanowires,  $\mu_{eff}$  was reduced by a factor of eight as *L* increased from 5 to 25  $\mu$ m. These channel length effects are attributed to the presence of defects including breaks and constrictions within individual pc-CdSe nanowires.

KEYWORDS: NWFET, mobility, lithography, electrodeposition, annealing, channel length

## **INTRODUCTION**

Field-effect transistors based upon semiconductor nanowires (NWFETs) were first prepared from semiconducting carbon nanotubes by Avouris<sup>1</sup> and Dekker<sup>2</sup> and coworkers in 1998. In 2000, Lieber and coworkers<sup>3</sup> prepared the first NWFETs from single crystalline silicon nanowires. Soon thereafter, a comparison of silicon NWFET transport metrics with their thin film counterparts<sup>4</sup> showed that the performance of NWFETs could substantially exceed that of thin film transistors (TFTs). This is one reason that the semiconductor industry is actively pursuing NWFET technology.<sup>5</sup>

Cadmium selenide (CdSe) is an n-type semiconductor ( $E_g = 1.70 \text{ eV}$ ) that has moderately high electron mobilities of  $\mu_{\text{eff}} = 650-800 \text{ cm}^2/(\text{V s})$  at 298 K.<sup>6,7</sup> CdSe is of interest because of its utility in photonic devices such as photodetectors, <sup>8-12</sup> light emitting diodes,<sup>13</sup> and solar cells.<sup>14–17</sup> FETs based upon polycrystalline CdSe thin films<sup>18–21</sup> and NWFETs based upon single crystalline CdSe nanowires<sup>22–27</sup> have both been studied (Table 1). Electron mobilities in thin film CdSe transistors (TFTs) have ranged from 0.02 cm<sup>2</sup>/(V s)<sup>21</sup> to 15 cm<sup>2</sup>/(V s),<sup>19</sup> and CdSe NWFETs have produced comparable electron mobilities on average, but across a wider range from 5 × 10<sup>-4</sup> cm<sup>2</sup>/(V s)<sup>23</sup> to 800 cm<sup>2</sup>/(V s).<sup>27</sup> The latter value,<sup>27</sup> which equals the bulk electron mobility in CdSe, is especially remarkable since it is nearly a factor of 100 higher than the electron mobilities measured in any other investigation of CdSe NWFETs (Table 1).

All of the CdSe NWFETs reported until now have been prepared from single crystalline nanowires synthesized using "bottom-up" methods, such as vapor-liquid-solid (VLS)

growth.<sup>28,29,3,30</sup> For these nanowires, fabrication of a NWFET requires the isolation of a single nanowire, or ensembles of oriented nanowires, starting from a powder of orientationally disordered nanowires. This tedious process involves the spin coating of nanowires at low coverage onto a substrate followed by the application of metal contacts to each nanowire using electron beam lithography (EBL).<sup>3</sup> In the case of nanowire arrays, additional processing steps are required to impart some degree of alignment to ensembles of nanowires. This can be accomplished, for example, by preparing source and drain electrodes and using dielectrophoresis to migrate nanowires in solution into the channel between these two electrodes.<sup>31-34</sup> NWFETs have also been achieved using "top-down" processing starting with CMOS-compatible silicon-on-insulator (SOI) wafers, isolating a nanowire using a combination of EBL and etching, and finally applying a top gate to the nanowire.<sup>35–37</sup> Top-down processing has the advantage that the orientation and doping of the nanowire can be precisely controlled, but slow EBL is still required to produce nanowires with widths in the sub 200 nm range from SOI wafers.

In this paper, we describe the preparation of NWFETs prepared from arrays of polycrystalline CdSe (pc-CdSe) nanowires. With the exception of silicon,<sup>38–40</sup> NWFETs have not been prepared from pc nanowires or nanowire arrays until now. These pc-CdSe nanowires were synthesized using the lithographically patterned nanowire electrodeposition (LPNE)

Received: July 11, 2012 Accepted: September 7, 2012 Published: September 7, 2012

ACS Publications © 2012 American Chemical Society

|                                                   | $L (\times W)^b$          | $\mu_{ m eff}$                   | $V_{ m th}$ | S                   |          |

|---------------------------------------------------|---------------------------|----------------------------------|-------------|---------------------|----------|

| description <sup>a</sup>                          | (µm)                      | $(cm^2/(V s))$                   | (V)         | (mV/dec)            | ref      |

| pc thin film CdSe tf                              | 8<br>(× 293)              | 1                                | 6.7         | 7000-10000          | 18       |

| pc thin film CdSe tf                              | (× 293)<br>100<br>(× 500) | 1-6.7                            | 2.5-30      | 260-5000            | 20       |

| pc thin film CdSe tf                              | 20<br>(× 200)             | 15                               | 3.5         | 500                 | 19       |

| nc thin film CdSe tf                              | 100-200<br>(× 1-2 mm)     | 0.02-0.6                         |             | 60                  | 21       |

| sc CdSe nr                                        | 3.2                       | 9.6                              | 20.9        |                     | 25       |

| sc CdSe nw                                        | 1                         | 0.5                              |             |                     | 22       |

| sc CdSe nw                                        | 18.3                      | 0.77                             |             |                     | 26       |

| sc CdSe nw                                        | 2                         | $5 \times 10^{-4}$               |             |                     | 23       |

| sc In-doped CdSe nw                               | 2                         | 0.1-6.7                          |             |                     | 23       |

| sc Cd-doped CdSe nr                               | 20                        | 800                              | -4.1        | 65                  | 27       |

| sc In-doped CdSe nw<br>pc CdSe nw: <sup>c</sup>   | 5                         | 3.2–166                          | -1.7-(-40)  | 508-10 <sup>6</sup> | 24       |

| annealed only <sup>d</sup>                        | 5                         | $1.9 (\pm 0.2) \times 10^{-4}$   | 18-25       | 3600                | this wor |

| CdCl <sub>2</sub> treated & annealed <sup>e</sup> | 5                         | 23 ( $\pm$ 5) × 10 <sup>-4</sup> | 4-8         | 2300                | this wor |

<sup>*a*</sup>Abbreviations: pc = polycrystalline, tf = thin film, sc = single crystalline, nw = nanowire, nr = nanorod. <sup>*b*</sup>Channel length,*L*, and width,*W*. All samples undoped unless otherwise specified. <sup>*c*</sup>NWFETs contained 100 (± 5) pc-CdSe nanowires. <sup>*d*</sup>Samples were thermally annealed at 300 °C for 4 h in N<sub>2</sub>. <sup>*c*</sup>Samples were treated by immersing for 10 s in saturated CdCl<sub>2</sub> in methanol and then thermally annealing at 300 °C for 4 h in N<sub>2</sub>.

method<sup>41-43</sup> which provides a means for patterning pc-CdSe nanowires across wafer-scale regions of a surface.<sup>11,12</sup> We compare pc-CdSe nanowires that were subjected to either of two post-processing treatments. All samples were thermally annealed at 300 °C × 4 h in nitrogen, but some nanowires were first exposed to CdCl<sub>2</sub> in methanol. CdCl<sub>2</sub> is a grain growth promoter for cadmium chalcogenides<sup>44,45,14</sup> and a chlorine dopant source.<sup>46</sup> We compare the properties of CdCl<sub>2</sub>-treated and untreated pc-CdSe nanowires and the performance of arrays of CdCl<sub>2</sub>-treated and untreated pc-CdSe nanowires in NWFETs.

## EXPERIMENTAL SECTION

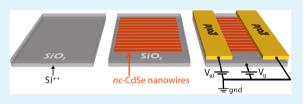

Nanowire Fabrication. The preparation of pc-CdSe nanowires on glass surfaces using the LPNE method has been described in detail previously.<sup>12,11</sup> In the first step of the LPNE process, a nickel layer is thermally evaporated onto RCA-cleaned, oxidized silicon substrates, SiO<sub>2</sub> (300 nm)/ Si(p<sup>+</sup>). Then a (+)-photoresist (PR) layer (Shipley 1808) is spin-coated, photopatterned, and developed, and the exposed nickel is removed by nitric acid etching. The etching duration is adjusted to produce an undercut around 300 nm in width at the edges of the exposed PR. This undercut produces a horizontal trench with a precisely defined height equal to the thickness of the Ni layer. Within this trench, pc-CdSe nanowires were electrodeposited using the scanning electrodeposition/stripping method, also as previously described.<sup>12,11,47-49</sup> The aqueous plating solution was unstirred aqueous 0.30 M CdSO<sub>4</sub>, 0.70 mM SeO<sub>2</sub>, and 0.25 M  $H_2SO_4$  at pH 1–2. In addition to the LPNE-patterned nickel electrode, a saturated calomel reference electrode (SCE) and a 2 cm<sup>2</sup> platinum foil counter electrode were also employed in conjunction with a one-compartment three-electrode electrochemical cell and a Gamry G300 potentiostat. pc-CdSe was deposited by scanning the potential of the lithographically patterned Ni edge from -0.4 to -0.8 V vs SCE at 50 mV/s. On the initial negative scan from -0.4 to -0.8 V, CdSe was electrodeposited on the nickel electrode

together with excess elemental cadmium. On the subsequent positive-going scan, excess elemental cadmium was oxidatively stripped from the nascent nanowire leaving stoichiometric CdSe (Figure 1b). A total of three scans were used to prepare the 60 nm (h)  $\times$  ~150 nm (w) pc-CdSe nanowires incorporated into transistors in this study. After the electrodeposition process was complete, the lithographically patterned nickel electrode and the associated PR were both removed using nitric acid and acetone, respectively. Arrays of 100 linear pc-CdSe nanowires were patterned at 5  $\mu$ m pitch onto the SiO<sub>2</sub>/Si substrate (Figure 1e,f). pc-CdSe nanowires were treated using either of two post-deposition processes:<sup>12,11</sup> (1) thermal annealing at 300°C for 4 h in N<sub>2</sub> or (2) exposure to saturated  $CdCl_2$  in methanol solution<sup>12,11,50,14,51</sup> for 10 s, followed by thermal annealing at 300  $^{\circ}$ C for 4 h in N<sub>2</sub>. After thermal annealing, these pc-CdSe nanowires were rinsed with Milli-Q water to remove residual CdCl<sub>2</sub>.

**Device Fabrication.** Lithographically patterned pc-CdSe nanowires were electrodeposited on highly doped p-type silicon substrates that were coated with 300 nm thermally grown gate oxide. Gold source and drain electrodes Au/Cr (50 nm/1 nm) were patterned onto both ends of the pc-CdSe nanowires by a photolithography and lift-off process (Figure 1d). The underlying conducting Si (resistivity:  $0.001-0.004 \ \Omega \text{ cm}$ ) was used as a back gate. Devices with three channel lengths, *L*, were evaluated: 5 (Figure 1e), 10, and 25  $\mu$ m. Measurements were conducted in a common source configuration (Figure 1a, right).

**pc-CdSe Characterization.** Scanning electron microscopy (SEM) images were acquired using a Philips XL-30 FEG (field emission gun) SEM using an accelerating voltage of 10 keV. All samples were sputtered with a thin layer of Au/Pd prior to imaging to prevent charging. Grazing-incidence X-ray diffraction (GIXRD) patterns were obtained using a Rigaku Ultima III high-resolution X-ray diffractometer employing the parallel beam optics with a fixed incident angle of 0.30°. The X-ray generator was operated at 40 kV and 44 mA with Cu K $\alpha$

**Figure 1.** Fabrication of pc-CdSe NWFETs. (a) Schematic diagram depicting the three-step NWFET fabrication process starting with a SiO<sub>2</sub>covered p<sup>+</sup>-silicon surface (left). An array of pc-CdSe nanowires is then prepared using LPNE (middle). Finally, gold source and drain electrodes are patterned by photolithography (right). (b) Current versus potential traces at 50 mV/s for the synthesis by scanning electrodeposition/stripping of pc-CdSe nanowires within the LPNE template electrode. The plating solution contains 0.30 M CdSO<sub>4</sub>, 0.70 mM SeO<sub>2</sub>, and 0.25 M H<sub>2</sub>SO<sub>4</sub> at pH 1– 2. (c) Raman scattering spectra ( $\lambda_{ex} = 532$  nm) of a pc-CdSe nanowire array on glass (orange trace) and a clean glass surface (black trace). (d–f) Scanning electron microscopy (SEM) images of the electrical contacts and contact pads (d), the 5  $\mu$ m channel showing five CdSe nanowires (horizontal) (e) and a single CdSe nanowire. The growth direction for this nanowire was from top to bottom (f).

irradiation. The JADE 7.0 X-ray pattern data processing software (Materials Data, Inc.) was used to analyze acquired patterns and estimate the respective grain diameter size. Raman spectra were collected using a Renishaw inVia Raman Microscope equipped with the Easy-Confocal optical system (spatial resolution less than 1  $\mu$ m) using a 532 nm laser and a 2400 line/mm grating. An optical power of 50 mW was used in conjunction with an integration time of 30 s. WiRE 3 software was used to acquire the data and images. Atomic force microscopy (AFM) images were acquired using an Asylum Research, MFP-3D AFM equipped with Olympus, AC160TS tips in a laboratory air ambient.

**NWFET Electrical Characterization.** Electrical characteristics of pc-CdSe NWFETs were measured using a Keithley 2400 sourcemeter and a Keithley 428 current amplifier both controlled by LabVIEW software. The source-drain current,  $I_{\rm sd}$ , was measured as a function of the source-drain voltage,  $V_{\rm sd}$ , at gate voltages,  $V_{\rm g'}$  ranging from -10 to 60 V. Values of the transconductance,  $g_{\rm m}$ , and the threshold voltage,  $V_{\rm th}$ , were determined from  $I_{\rm sd}$  versus  $V_{\rm gs}$  curves using the linear region of these curves<sup>25,27</sup>

$$g_{\rm m} = \frac{dI_{\rm sd}}{dV_{\rm gs}} \tag{1}$$

For CdSe nanowires with a rectangular cross section, the gate capacitance per unit length can be calculated using eq  $2^{52}$

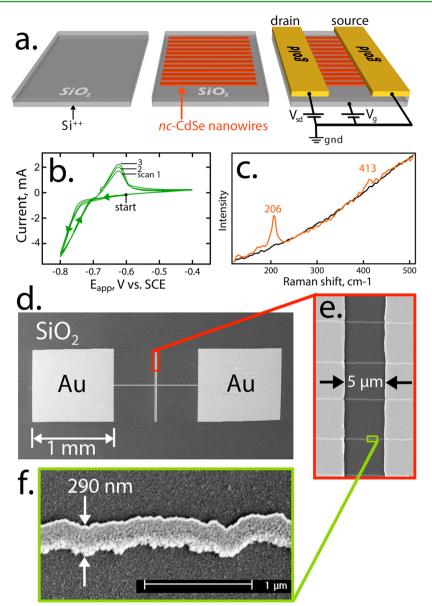

**Figure 2.** (a,d) SEM images and atomic force microscopy (AFM) images (b,e) of as-deposited pc-CdSe nanowires that were thermally annealed (300 °C, 4 h,  $N_2$ ) (a,b) and pc-CdSe nanowires dipped in saturated CdCl<sub>2</sub>, methanol solution (10 s), and thermally annealed (300 °C, 4 h,  $N_2$ ) (d,e). (c,f) Grazing incidence X-ray diffraction (GIXRD) patterns of: (c) as-deposited pc-CdSe nanowires that were thermally annealed (300 °C, 4 h,  $N_2$ ), (f) dipped in saturated CdCl<sub>2</sub>, methanol solution (10 s) and annealed (300 °C, 4 h,  $N_2$ ).

$$C = \varepsilon_{0}\varepsilon_{r} \left[ \frac{w - t/2}{h} + \frac{2\pi}{\ln(1 + 2h/t + \sqrt{2h/t(2h/t + 2))}} \right]$$

(2)

where *w* is the mean width of the nanowires; *t* is the mean height; and *h* is the gate oxide thickness (300 nm). Linear range carrier mobilities,  $\mu_{\text{eff}}$ , were estimated according to eq 3.<sup>22,23,27,53</sup>

$$\mu_{\rm eff} = \frac{g_{\rm m}L^2}{NCV_{\rm sd}} \tag{3}$$

where N is the number of nanowires. The electron carrier concentrations,  $n_{e}$ , were estimated from the equation<sup>54,27</sup>

$$n_{\rm e} = \frac{CV_{\rm th}}{ewtL} \tag{4}$$

Threshold voltage  $V_{\rm th}$  was estimated from the linear region of the  $I_{\rm sd}$  versus  $V_{\rm gs}$  plot by extrapolation to the abscissa.<sup>6,18,25</sup> The subthreshold slope, *S*, was calculated from transfer curves in the interval  $V_{\rm th} < V_{\rm gs} < (V_{\rm th} + 4 \text{ V})$  according to<sup>6</sup>

$$S = \frac{dV_{\rm gs}}{d(\log I_{\rm sd})} \tag{5}$$

The on-off current ratio  $I_{\rm on}/I_{\rm off}$  was obtained from the logarithmic plot of  $I_{\rm sd}$  versus  $V_{\rm gs}$  where  $I_{\rm on}$  is the current value at the threshold voltage and  $I_{\rm off}$  is the current value when the device is in the off state.<sup>25</sup>

#### RESULTS AND DISCUSSION

**Synthesis and Characterization of pc-CdSe Nano-wires.** Arrays of pc-CdSe nanowires prepared using LPNE were used as the starting point for the fabrication of NWFETs in this study (Figure 1a). As previously described,<sup>11,12</sup> stoichiometric pc-CdSe nanowires were obtained using the

scanning electrodeposition/stripping method.<sup>47</sup> An aqueous plating solution containing 0.30 M CdSO<sub>4</sub>, 0.70 mM SeO<sub>2</sub>, and 0.25 M H<sub>2</sub>SO<sub>4</sub> at pH  $1-2^{49,55}$  was used to electrodeposit both CdSe and elemental cadmium on an initial negative-going voltammetric scan from -0.60 to -0.80 V vs SCE. The electrodeposition of elemental selenium, although thermodynamically possible, does not occur because the Cd:Se ratio in this plating solution is 43:1. As the potential is scanned positively from -0.80 V (Figure 1b), excess elemental Cd is removed from the nascent pc-CdSe nanowires at -0.62 V to produce nanowires of near stoichiometric pc-CdSe. Asdeposited pc-CdSe nanowires prepared by LPNE did not show a gate effect in spite of the fact that the electrical conductivity of these nanowires is just  $\sim 20\%$  higher than for CdSe nanowires that were thermally annealed at 300  $^{\circ}$ C × 4 h in nitrogen and which did demonstrate a gate effect (vide infra).<sup>12</sup> For this reason, all pc-CdSe nanowires examined in this study were subjected to thermal annealing, but some nanowires were exposed to saturated CdCl<sub>2</sub> in methanol before this thermal treatment. Exposure to CdCl<sub>2</sub> in methanol prior to thermal annealing has been shown to promote grain growth in CdSe,<sup>44,45,14</sup> and it has also been used as a chlorine dopant source.<sup>46</sup> Recently,<sup>11,12</sup> we found that  $CdCl_2$  treatment increases both the mean grain diameter and the photoconductive gain for arrays of pc-CdSe nanowires configured as photodetectors.

Arrays of pc-CdSe nanowires were characterized using scanning electron microscopy (SEM), atomic force microscopy (AFM), X-ray diffraction (XRD), and Raman spectroscopy before the patterning of gold source and drain electrodes. Raman spectra acquired using  $\lambda_{ex} = 532$  nm were identical for pc-CdSe nanowires that were treated with CdCl<sub>2</sub> (wurzite phase) and those that were not (zinc blende phase). In both cases, transitions at 206 and 413 cm<sup>-1</sup>, assigned to the longitudinal optical (LO) phonon and to 2LO, respectively,

| Table 2. Performance Metric | for NWFETs Prepared | l Using Lithographical | ly Patterned po | c-CdSe Nanowire Arrays" |

|-----------------------------|---------------------|------------------------|-----------------|-------------------------|

|-----------------------------|---------------------|------------------------|-----------------|-------------------------|

| L                                                                        | $n_e^b$                        | $\mu_{	ext{eff}}{}^c$           | $V_{ m th}$ | S <sup>d</sup> | C <sup>e</sup> | $g_{\rm m}^{f}$ |                          |  |

|--------------------------------------------------------------------------|--------------------------------|---------------------------------|-------------|----------------|----------------|-----------------|--------------------------|--|

| (µm)                                                                     | $(cm^{-3})$                    | $(cm^2/(V s))$                  | (V)         | (mV/dec)       | (fF)           | (nS)            | $I_{\rm on}/I_{\rm off}$ |  |

| thermally annealed <sup>g</sup>                                          |                                |                                 |             |                |                |                 |                          |  |

| 5                                                                        | $1.8 (\pm 0.3) \times 10^{18}$ | $1.9 (\pm 0.2) \times 10^{-4}$  | 18-25       | 3600           | 0.39           | 0.046           | ~80                      |  |

| 10                                                                       | $3.6 (\pm 0.1) \times 10^{18}$ | $6 (\pm 2) \times 10^{-5}$      | 42-46       | 4800           | 0.78           | 0.02            | ~75                      |  |

| 25                                                                       | $3.6 (\pm 0.3) \times 10^{18}$ | $8 (\pm 3) \times 10^{-6}$      | 50-60       | 7100           | 1.6            | 0.0005          | ~40                      |  |

| treated with CdCl <sub>2</sub> /MeOH and thermally annealed <sup>h</sup> |                                |                                 |             |                |                |                 |                          |  |

| 5                                                                        | $5(\pm 2) \times 10^{17}$      | $23 (\pm 5) \times 10^{-4}$     | 4-8         | 2300           | 0.39           | 0.76            | ~320                     |  |

| 10                                                                       | $10 \ (\pm 2) \times 10^{17}$  | 9 ( $\pm$ 5) × 10 <sup>-4</sup> | 10-15       | 3300           | 0.78           | 0.06            | ~240                     |  |

| 25                                                                       | $1.3 (\pm 0.3) \times 10^{18}$ | $3(\pm 2) \times 10^{-4}$       | 17-25       | 4500           | 1.6            | 0.009           | ~210                     |  |

<sup>*a*</sup>NWFETs contained 100 ( $\pm$  5) pc-CdSe nanowires. <sup>*b*</sup>Electron concentration. <sup>*c*</sup>Linear range electron mobility. <sup>*d*</sup>Subthreshold slope, with units of voltage per decade current. <sup>*c*</sup>Capacitance. <sup>*f*</sup>Transconductance. <sup>*g*</sup>Samples were thermally annealed at 300 °C for 4 h in N<sub>2</sub>. <sup>*h*</sup>Samples were treated by immersing for 10 s in saturated CdCl<sub>2</sub> in methanol and then thermally annealing at 300 °C for 4 h in N<sub>2</sub>.

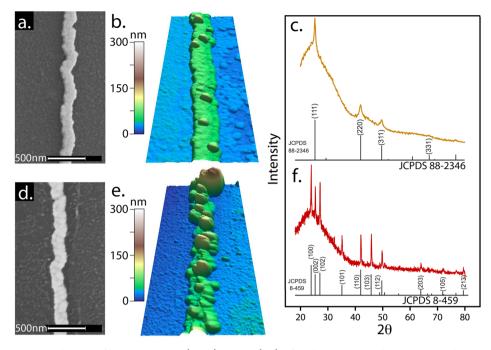

**Figure 3.** Electrical characterization of  $L = 5 \ \mu m$  NWFETs based on pc-CdSe nanowire arrays. Shown in (a,b,c) are data for nanowires that were not treated with CdCl<sub>2</sub> and in (d,e,f) are data for CdCl<sub>2</sub>-treated nanowires: (a,d)  $I_{sd}$  versus  $V_{sd}$  traces as a function of  $V_{gs}$ . (b,e)  $I_{sd}$  versus  $V_{gs}$  transfer characteristics for three  $V_{sd}$  values and (c,f) log-linear plot of the same data shown in (b,e).

were observed (Figure 1c), in accordance with prior work on CdSe.<sup>56,57</sup> This spectrum is consistent with CdSe since the LO phonon energy for CdSe single crystals is 209 cm<sup>-1</sup> whether these crystal structures are wurtzite or zinc blende.<sup>58</sup>

The influence of the  $CdCl_2$  treatment is apparent in scanning electron microscope (SEM) and atomic force microscope (AFM) images of these pc-CdSe nanowires (Figure 2). Both SEM (Figure 2a,d) and AFM (Figure 2b,e) analysis show that  $CdCl_2$  treatment causes roughening of the nanowire surface as a consequence of rapid grain growth. Especially clear in AFM images of  $CdCl_2$ -treated pc-CdSe nanowires are individual CdSe grains (Figure 2e). Grazing-incidence X-ray diffraction (GIXRD) analysis was performed on pc-CdSe nanowires, and the mean grain diameter,  $d_{ave}$ , was estimated from the X-ray line width using the Scherrer equation<sup>59</sup>

$$d_{\rm ave} = 0.89 \frac{\gamma}{B\cos\theta} \tag{6}$$

where  $\gamma$  is the X-ray wavelength; *B* is the full width of the peak measured at half-height; and  $\theta$  is the diffraction angle. GIXRD patterns for pc-CdSe nanowires that were not treated with CdCl<sub>2</sub> (Figure 2c) show three reflections assignable to a zinc blende structure. Line broadening permits an estimate of  $d_{ave} =$ 10 nm. A completely different GIXRD pattern, assignable to wurtzite CdSe, is observed for CdCl<sub>2</sub>-treated pc-CdSe nanowires. The narrower lines in this pattern correspond to  $d_{ave} =$  80 nm. The influence of the CdCl<sub>2</sub> treatment on the grain

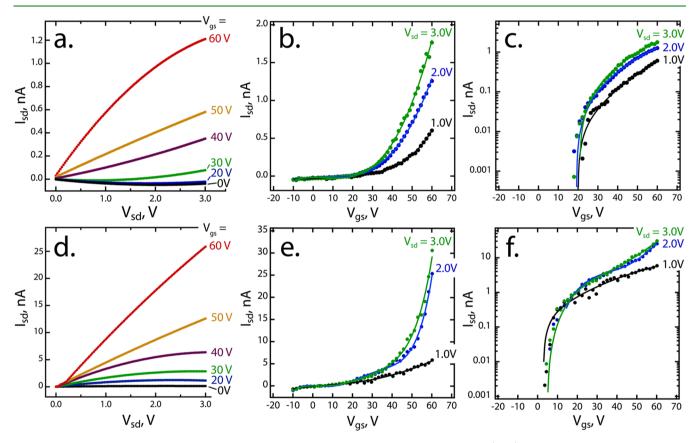

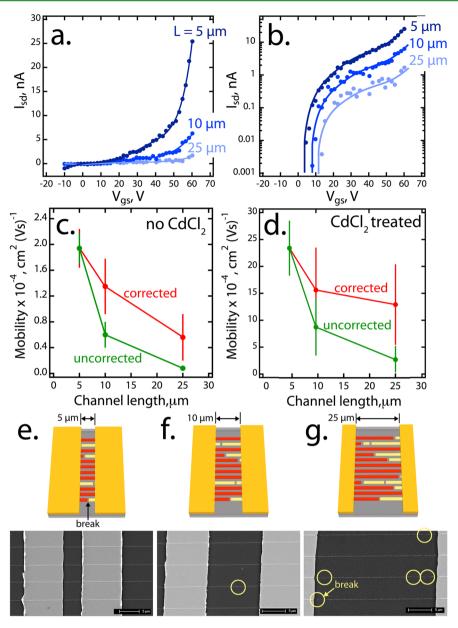

**Figure 4.** Influence of the channel length, *L*, on the transfer characteristics for  $CdCl_2$ -treated and annealed pc-CdSe NWFETs. (a)  $I_{sd}$  versus  $V_{gs}$  plots at  $V_{sd} = 2$  V for three channel lengths as indicated. (b) log  $I_{sd}$  versus  $V_{gs}$  curves for three channel lengths as indicated. (c) Linear range carrier mobilities,  $\mu_{eff}$  versus channel length for pc-CdSe NWFETs not treated with CdCl<sub>2</sub> before (green trace) and after (red trace) correcting for discontinuous nanowires. (d) Same plot as (c) for pc-CdSe NWFETs that were CdCl<sub>2</sub> treated. (e–g) Schematic diagrams of NWFET devices (top) and SEM images (bottom) for  $L = 5 \mu m$  (d),  $L = 10 \mu m$  (e), and  $L = 25 \mu m$  (f) showing an increase in the number of discontinuities with increasing *L*.

diameter and the crystal structure are consistent with our previous results  $^{11,12}$  as well as the previous works of others.  $^{60-63}$

The electrical properties of pc-CdSe NWFETs were examined for devices containing 100 ( $\pm$ 5) nanowires having three different channel lengths: 5, 10, and 25  $\mu$ m. Performance metrics for these devices are summarized in Table 2. In a common source configuration (Figure 1a, right), the application of positive  $V_{\rm gs}$  strongly enhances  $I_{\rm sd}$  versus  $V_{\rm sd}$  both for CdCl<sub>2</sub>-untreated (Figure 3a) and CdCl<sub>2</sub>-treated (Figure 3d) pc-CdSe nanowires. These output characteristics are consistent with enhancement mode operation for an n-type channel,<sup>6</sup> just as previously reported for FETs prepared from

polycrystalline CdSe  $\mathrm{films}^{18-21}$  and single crystalline CdSe nanowires.  $^{25,22,26,23,27,24}$

Transfer characteristics for the same two devices shown in Figure 3a,d show a threshold voltage of 18–25 V for CdCl<sub>2</sub>untreated (Figure 3b,c) nanowires and 4–8 V for CdCl<sub>2</sub>treated (Figure 3e,f) pc-CdSe nanowires. These voltage ranges reflect the device-to-device variability in  $V_{\rm th}$  for 3–5 NWFETs at each channel length value. The threshold voltage for a CdSe NWFET has been reported in just one previous study to our knowledge:  $V_{\rm th}$  = 20.9 V was observed by Lee and coworkers<sup>25</sup> for NWFETs (L = 3.2  $\mu$ m) prepared from individual undoped single crystalline CdSe nanoribbons (width = 630 nm) synthesized by evaporation. Several studies involving thin film pc-CdSe FETs have achieved lower  $V_{\rm th}$  values<sup>18–20</sup> ranging from 2.5<sup>20</sup> to 6.7 V<sup>18</sup> (Table 1). This performance pertains to devices prepared from undoped CdSe. With intentional doping by either cadmium<sup>27</sup> or indium,<sup>24</sup>  $V_{\rm th}$  shifts sharply to voltages as negative as -40 V.<sup>27</sup>

The sensitivity of a FET to gate inputs just below  $V_{\rm th}$  is measured by the subthreshold slope, S, defined as the change in the gate voltage necessary to induce a change in the sourcedrain current by one order of magnitude.<sup>6</sup> Conventional silicon FETs produce S = 60-70 mV/dec,<sup>6</sup> and performance of this caliber has been achieved for CdSe devices in two previous studies—one involving pc-CdSe thin film FETs prepared from CdSe nanocrystals<sup>21</sup> and a second for cadmium-doped NWFETs.<sup>27</sup> S has not been measured and reported for NWFETs prepared from undoped CdSe nanowires, to our knowledge (Table 1). Conventional thin film FETs (not prepared from CdSe nanocrystals) display much higher S values<sup>18-20</sup> ranging from 500 mV/dec<sup>19</sup> to 10 V/dec.<sup>18</sup> For the pc-CdSe NWFETs prepared in this study, S was in the range from 2.3 to 7.1 V/dec. Lower S values were associated with NWFETs prepared from CdCl<sub>2</sub>-untreated nanowires (Table 1). These are the first and only S values that have been reported for NWFETs prepared from undoped CdSe nanowires.

Device metrics for these NWFETs are strongly influenced by the channel length, *L*, for both CdCl<sub>2</sub>-untreated and treated NWFETs (Table 2, Figure 4). As compared with NWFETs having  $L = 5 \ \mu m$ , NWFETs with  $L = 10 \ \mu m$  and 25  $\ \mu m$  show higher  $V_{\rm th}$  (Figure 4b) and *S*, while the  $g_{\rm m}$  and  $I_{\rm on}/I_{\rm off}$  are both substantially reduced (Figure 4a,b). Electron mobilities,  $\mu_{\rm eff}$ ; were also reduced with increasing *L*, decreasing from 2 (±0.5) × 10<sup>-3</sup> cm<sup>2</sup>/(V s) at  $L = 5 \ \mu m$  to 3 (±2) × 10<sup>-4</sup> cm<sup>2</sup>/(V s) for  $L = 25 \ \mu m$  for CdCl<sub>2</sub>-treated NWFETs, for example (Figure 4d, green trace).

One reason for the depression in  $\mu_{\rm eff}$  with increasing L is discontinuities in these nanowires, as shown schematically in Figure 4e-g (top). SEM images (Figure 4e,f, bottom) reveal the presence of discontinuities (circles) in some of the nanowires present in the longer L = 10 and 25  $\mu$ m channels. Although Figure 4e,f shows data for CdCl<sub>2</sub>-treated nanowires, these breaks were also observed in untreated pc-CdSe NWFETs, and a similar depression in  $\mu_{\text{eff}}$  was observed in this case (Figure 4c). The majority of these breaks is formed because of stresses applied to the nanowires during the processing steps that succeed annealing, especially the photolithographic patterning of the gold contacts. A similar decrease in  $\mu_{\rm eff}$  with channel length was also observed by Unalan et al.<sup>64,65</sup> for ZnO NWFETs. We used SEM to determine the number of broken nanowires in our FETs. When the electrically discontinuous nanowires are removed from the total *N* in eq 3,  $\mu_{\text{eff}}$  increases by a factor of ~3 for the 10 and 25  $\mu$ m channels, but the corrected  $\mu_{\rm eff}$  values (Figures 4c,d, red trace) remain below the values measured for  $L = 5 \ \mu m$ NWFETs. These data also show that the depression in  $\mu_{\text{eff}}$  is not confined to CdCl<sub>2</sub>-treated nanowires; a similar effect is seen for nontreated nanowires (Figure 4c). Our hypothesis is that the depression of  $\mu_{\rm eff}$  for longer channels is caused by the presence of constrictions in the nanowires that are formed during the thermal annealing process. If this is correct, then a remedy might involve the encapsulation of the as-deposited CdSe nanowires in an insulating shell of SiO<sub>2</sub> or another dielectric using atomic layer deposition prior to annealing, to suppress these morphology changes thereby increasing  $\mu_{\text{eff}}$  for these long channel NWFETs.

## CONCLUSION

In this paper, we have realized transistors based upon arrays of polycrystalline CdSe nanowires. Uniquely, the LPNE method used to prepare these nanowire arrays permits the patterning of nanowires using photolithography across wafer-scale regions. Two post-processing treatments for these nanowires were compared-the first consisting of thermal annealing only and the second involving exposure to methanolic CdCl<sub>2</sub>, a grain growth promoter, followed by thermal annealing. The influence of the CdCl<sub>2</sub> treatment was significant, increasing the mean grain diameter in pc-CdSe nanowires by a factor of eight from 10 to 80 nm. For both CdCl<sub>2</sub>-treated and untreated nanowires, the application of a positive gate voltage strongly enhanced conduction; however, NWFETs prepared from CdCl<sub>2</sub>-treated nanowires showed improved performance highlighted by a reduction in the threshold voltage ( $\sim$ 70%) and the subthreshold slope (~35%), while the  $I_{\rm op}/I_{\rm off}$  ratio was increased by a factor of 3-4. The resulting performance metrics for CdCl<sub>2</sub>-treated NWFETs are comparable or superior to those of polycrystalline CdSe film-based FETs, but lower  $\mu_{eff}$ values were obtained for our nanowire devices. A pronounced channel length effect on  $\mu_{\rm eff}$  suggests that defects in these nanowires such as constrictions may contribute to the depressed electron mobilities. This study demonstrates that highly miniaturized transistors based upon lithographically patterned, electrodeposited polycrystalline nanowires can be prepared.

### AUTHOR INFORMATION

### **Corresponding Author**

\*E-mail: rmpenner@uci.edu.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

The authors gratefully acknowledge the financial support of this work by the National Science Foundation (DMR-1206867). All electron microscopy was carried out in the Laboratory for Electron and X-ray Instrumentation (LEXI) at the University of California, Irvine.

#### REFERENCES

(1) Martel, R.; Schmidt, T.; Shea, H.; Hertel, T.; Avouris, P. Appl. Phys. Lett. **1998**, 73, 2447–2449.

(2) Tans, S.; Verschueren, A.; Dekker, C. Nature 1998, 393, 49–52.

(3) Cui, Y.; Duan, X.; Hu, J.; Lieber, C. J. Phys. Chem. B 2000, 104, 5213–5216.

(4) Cui, Y.; Zhong, Z.; Wang, D.; Wang, W.; Lieber, C. Nano Lett. 2003, 3, 149–152.

(5) http://www.itrs.net/Links/2009ITRS/Home2009.htm (accessed 2009).

(6) Sze, S. M. Semiconductor devices, physics and technology, 2nd ed.; Wiley: New York, 2002.

(7) Streetman, B. G.; Banerjee, S. *Solid state electronic devices*, 6th ed.; Pearson/Prentice Hall: Upper Saddle River, N.J., 2006.

(8) Oertel, D. C.; Bawendi, M. G.; Arango, A. C.; Bulovic, V. Appl. Phys. Lett. 2005, 87 (213505), 3pp.

(9) Jiang, Y.; Zhang, W. J.; Jie, J. S.; Meng, X. M.; Fan, X.; Lee, S.-T. Adv. Funct. Mater. 2007, 17, 1795–1800.

(10) Singh, A.; Li, X.; Protasenko, V.; Galantai, G.; Kuno, M.; Xing, H. G.; Jena, D. *Nano Lett.* **2007**, *7*, 2999–3006.

(11) Kung, S.-C.; van der Veer, W. E.; Yang, F.; Donavan, K. C.; Penner, R. M. *Nano Lett.* **2010**, *10*, 1481–1485.

#### **ACS Applied Materials & Interfaces**

(12) Kung, S.-C.; Xing, W.; van der Veer, W. E.; Yang, F.; Donavan, K. C.; Cheng, M.; Hemminger, J. C.; Penner, R. M. ACS Nano **2011**, *5*, 7627–7639.

(13) Schreuder, M. A.; Xiao, K.; Ivanov, I. N.; Weiss, S. M.; Rosenthal, S. J. *Nano Lett.* **2010**, *10*, 573–576.

(14) Birkmire, R. W.; Eser, E. Annu. Rev. Mater. Sci. 1997, 27, 625–653.

(15) Benamar, E.; Rami, M.; Fahoume, M.; Chraibi, F.; Ennaoui, A. *Ann. Chim.-Sci. Mater.* **1998**, 23, 369–372.

- (16) Lee, K.-S.; Kim, I.; Gullapalli, S.; Wong, M. S.; Jabbour, G. E. Appl. Phys. Lett. 2011, 99 (223515), 3pp.

- (17) Alamgir, K.; Pervaiz, T.; Arif, S. Energy Sources, Part A 2012, 34, 297–305.

(18) Ridley, B.; Nivi, B.; Jacobson, J. Science 1999, 286, 746-749.

- (19) Gan, F.; Shih, I. IEEE Trans Electron Devices 2002, 49, 15-18.

- (20) Byrne, P. D.; Facchetti, A.; Marks, T. J. Adv. Mater. 2008, 20, 2319-2324.

(21) Kang, M. S.; Sahu, A.; Norris, D. J.; Frisbie, C. D. *Nano Lett.* **2010**, *10*, 3727–3732.

(22) Skinner, K.; Dwyer, C.; Washburn, S. Appl. Phys. Lett. 2008, 92 (112105), 3pp.

- (23) He, Z.; Jie, J.; Zhang, W.; Zhang, W.; Luo, L.; Fan, X.; Yuan, G.; Bello, I.; Lee, S.-T. Small **2009**, *5*, 345–350.

- (24) He, Z.; Zhang, W.; Zhang, W.; Jie, J.; Luo, L.; Yuan, G.; Wang, J.; Wu, C. M. L.; Bello, I.; Lee, C.-S.; Lee, S.-T. *J. Phys. Chem. C* **2010**, *114*, 4663–4668.

- (25) Jie, J. S.; Zhang, W. J.; Jiang, Y.; Lee, S. T. Appl. Phys. Lett. 2006, 89 (133118), 3pp.

- (26) Yan, Y.; Liao, Z.-M.; Bie, Y.-Q.; Wu, H.-C.; Zhou, Y.-B.; Fu, X.-W.; Yu, D.-P. *Appl. Phys. Lett.* **2011**, *99* (103103), 3pp.

- (27) Liu, C.; Wu, P.; Sun, T.; Dai, L.; Ye, Y.; Ma, R.; Qin, G. J. Phys. Chem. C 2009, 113, 14478-14481.

- (28) Westwater, J.; Gosain, D.; Tomiya, S.; Usui, S.; Ruda, H. J. Vac. Sci. Technol., B 1997, 15, 554–557.

- (29) Westwater, J.; Gosain, D.; Usui, S. Jpn. J. Appl. Phys., Part 1 1997, 36, 6204-6209.

- (30) Wu, Y.; Yang, P. J. Am. Chem. Soc. 2001, 123, 3165-3166.

- (31) Smith, P.; Nordquist, C.; Jackson, T.; Mayer, T.; Martin, B.; Mbindyo, J.; Mallouk, T. *Appl. Phys. Lett.* **2000**, *77*, 1399–1401.

- (32) Hamers, R.; Beck, J.; Eriksson, M.; Li, B.; Marcus, M.; Shang, L.; Simmons, J.; Streifer, J. Nanotechnology **2006**, *17*, S280–S286.

- (33) Raychaudhuri, S.; Dayeh, S. A.; Wang, D.; Yu, E. T. Nano Lett. 2009, 9, 2260–2266.

- (34) Freer, E. M.; Grachev, O.; Duan, X.; Martin, S.; Stumbo, D. P. *Nat. Nanotechnol.* **2010**, *5*, 525–530.

- (35) Stern, E.; Klemic, J. F.; Routenberg, D. A.; Wyrembak, P. N.; Turner-Evans, D. B.; Hamilton, A. D.; LaVan, D. A.; Fahmy, T. M.;

- Reed, M. A. Nature 2007, 445, 519–522. (36) Chen, H.-Y.; Lin, C.-Y.; Chen, M.-C.; Huang, C.-C.; Chien, C.-

(36) Chen, H.-Y.; Lin, C.-Y.; Chen, M.-C.; Huang, C.-C.; Chien, C.-H. Jpn. J. Appl. Phys. **2011**, *50*, 04DL05.

(37) Chen, M.-C.; Chen, H.-Y.; Lin, C.-Y.; Chien, C.-H.; Hsieh, T.-F.; Horng, J.-T.; Qiu, J.-T.; Huang, C.-C.; Ho, C.-H.; Yang, F.-L. Sensors **2012**, *12*, 3952–3963.

(38) Lin, H.; Lee, M.; Su, C.; Huang, T.; Lee, C.; Yang, Y. *IEEE Electron Device Lett.* **2005**, *26*, 643–645.

(39) Lin, H.-C.; Lee, M.-H.; Su, C.-J.; Shen, S.-W. *IEEE Trans. Electron Devices* **2006**, *53*, 2471–2477.

- (40) Lin, H.-C.; Hsu, H.-H.; Su, C.-J.; Huang, T.-Y. *IEEE Electron Device Lett.* **2008**, *29*, 718–720.

- (41) Menke, E. J.; Thompson, M. A.; Xiang, C.; Yang, L. C.; Penner, R. M. Nat. Mater. **2006**, *5*, 914–919.

- (42) Xiang, C.; Kung, S.-C.; Taggart, D. K.; Yang, F.; Thompson, M. A.; Gueell, A. G.; Yang, Y.; Penner, R. M. *ACS Nano* **2008**, *2*, 1939–1949.

- (43) Xiang, C.; Yang, Y.; Penner, R. M. Chem. Commun. 2009, 859–873.

- (44) Rami, M.; Benamar, E.; Fahoume, M.; Chraibi, F.; Ennaoui, A. *M. J. Condens. Matter* **2000**, *3*, 66–70.

- (45) Ringel, S. A.; Smith, A. W.; MacDougal, M. H.; Rohatgi, A. J. Appl. Phys. **1991**, 70, 881–889.

- (46) Svechnic, S.; Shtrum, E.; Savialov, L.; Philippo, A.; Matchina, S.; Klochcov, V. *Thin Solid Films* **1972**, *11*, 33–41.

- (47) Kressin, A.; Doan, V.; Klein, J.; Sailor, M. Chem. Mater. 1991, 3, 1015–1020.

- (48) Klein, J.; Herrick, R.; Palmer, D.; Sailor, M.; Brumlik, C.; Martin, C. Chem. Mater. **1993**, *5*, 902–904.

(49) Schierhorn, M.; Boettcher, S. W.; Ivanovskaya, A.; Norvell, E.; Sherman, J. B.; Stucky, G. D.; Moskovits, M. J. Phys. Chem. C 2008, 112, 8516–8520.

(50) Rami, M.; Benamar, E.; Fahoume, M.; Chraibi, F.; Ennaoui, A. *M. J. Condens Matter* **2000**, *3*, 66–70.

- (51) Ndiaye, A.; Youm, I. Eur. Phys. J.: Appl. Phys. 2003, 23, 75-82.

- (52) Yuan, C.; Trick, T. IEEE Electron Device Lett. 1982, 3, 391-393.

(53) Suh, D.-I.; Lee, S.-Y.; Hyung, J.-H.; Kim, T.-R.; Lee, S.-K. J. Phys. Chem. C 2008, 112, 1276–1281.

- (54) Huang, Y.; Duan, X.; Cui, Y.; Lieber, C. Nano Lett. 2002, 2, 101–104.

- (55) Pena, D.; Mbindyo, J.; Carado, A.; Mallouk, T.; Keating, C.; Razavi, B.; Mayer, T. J. Phys. Chem. B **2002**, *106*, 7458–7462.

- (56) Venugopal, R.; Lin, P.; Liu, C.; Chen, Y. J. Am. Chem. Soc. 2005, 127, 11262–11268.

- (57) Kumar, S.; Kumar, V.; Sharma, S. K.; Sharma, S. K.; Chakarvarti, S. K. Superlattices Microstruct. **2010**, *48*, 66–71.

- (58) Chen, S.-F.; Liu, C.-P.; Eliseev, A. A.; Petukhov, D. I.; Dhara, S. Appl. Phys. Lett. **2010**, 96 (111907), 3pp.

- (59) Patterson, A. Phys. Rev. 1939, 56, 978-982.

(60) Bandaranayake, R.; Wen, G.; Lin, J.; Jiang, H.; Sorensen, C. Appl. Phys. Lett. **1995**, 67, 831–833.

- (61) Kale, R.; Lokhande, C. Semicond. Sci. Technol. 2005, 20, 1-9.

- (62) Farva, U.; Park, C. Sol. Energy Mater. Sol. Cells 2010, 94, 303–309.

(63) Portillo-Moreno, O.; Lozada-Morales, R.; Rubin-Falfan, M.; Perez-Alvarez, J.; Zelaya-Angel, O.; Banos-Lopez, L. J. Phys. Chem. Solids **2000**, 61, 1751–1754.

(64) Unalan, H. E.; Zhang, Y.; Hiralal, P.; Dalal, S.; Chu, D.; Eda, G.; Teo, K. B. K.; Chhowalla, M.; Milne, W. I.; Amaratunga, G. A. J. *Appl. Phys. Lett.* **2009**, *94* (163501), 3pp.

(65) Unalan, H. E.; et al. *IEEE Trans. Electron Devices* 2008, 55, 2988-3000.